1. High-Speed Signal Acquisition & Processing for Ultrasound Brain Imaging.

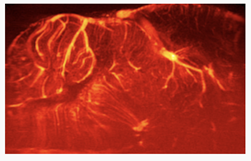

Functional ultra-sound (fUS) imaging is a powerful new modality that has emerged in the last decade and is capable of providing unprecedented functional images of the brain as sub-micrometer spatial and sub-neural-spiking temporal resolution. The CUBE multidisciplinary facility and the NeuroComputing Lab (NCL) of the Erasmus Medical Center, Rotterdam, are building novel fUS technology and are finally in possession of an imaging modality that can track in high detail the workings of the human brain. The unprecedented quality of fUS, which also has the potential to outperform mature modalities like fMRI, comes at the cost of large data sizes being generated. Currently, by using a 2D fUS acquisition probe, data is being generated at 6 GB/s.

To tackle this data deluge as well as other technical challenges, this MSc thesis topic aims at building an FPGA-based acquisition setup which will facilitate high ultrasound-channel counts (≥ 8 channels @ ≥ 12 bits/channel) at high sampling rates (10 – 30 MHz). The design-space exploration involves selecting the best-of-breed FPGA device to handle the data-rate needs, co-designing with a CPU (e.g. via SDAccel) to handle interfacing to the outside world and also deploying signal-processing and deep-learning algorithms for real-time fUS-image processing on-board. This research is being jointly conducted by the Erasmus Medical Center and the Delft University of Technology.

Keywords: FPGA acceleration, HPC, image processing, deep learning.

Prerequisites: FPGA design, signal processing (basic), C language, Vivado C language.

Optionally: Image processing, Machine learning, deep learning.

Contact: Christos Strydis

2. Hardware Acceleration of Compressing-Sensing Algorithms for Brain Imaging

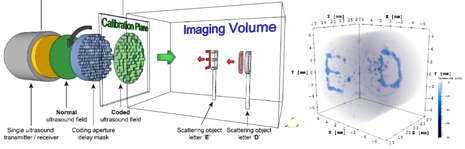

3D-dimensional ultrasound is a very powerful imaging technique, but it requires transducers that accommodate thousands of sensors and complex hardware which restricts its use to specialized clinical applications in developed countries. Manufacturing this type of transducers is complex and very costly. The CUBE multidisciplinary facility and the NeuroComputing Lab (NCL) of the Erasmus Medical Center, Rotterdam, have proposed a novel approach that can overcome this limitation and make 3D imaging simply available to any application by making use of a technique called compressive sensing. The main technological idea behind this technique is that a simple plastic coding mask is already enough to compress the 3D information in such a way that far less sensors are needed. This concept can be applied to extend the imaging capabilities of commercial ultrasound probes from 2D to 3D, but also opens up the possibility for a new type of wearable imaging device for long-time monitoring/imaging of the brain. Key to deploying this technology is the “inverse calculation” of the ultrasound deformations the plastic mask creates while imaging a target (here: neural tissue in living brains). This calculation involves, as a first step, solving a massive linear system of equations, in the range of 30 GB of data per new imaging target. Currency work in the lab involves porting this algorithm onto state-of-the-art GPUs, however we are severely limited by memory-capacity and low-latency concerns, since the system is a streaming, real-time setup.

The goal of this MSc thesis (two independent student topics) is to redeploy the compressive-sensing algorithms onto (a) a Xilinx FPGA, or (b) a Maxeler Dataflow Engine (DFE), for tackling both aforementioned problems. The design should also leave enough silicon space for also extending the algorithms with on-board deep-learning steps, for further image processing. Finally, these accelerated versions should be made to interface to the rest of the experimental setup involving data storage, database access and (offline) image processing. This research is being jointly conducted by the Erasmus Medical Center and the Delft University of Technology.

Keywords: HPC, FPGA acceleration, DFE acceleration, image processing, deep learning.

Prerequisites: FPGA design, signal processing (basic), C language, Vivado C language.

Optionally: CUDA programming, image processing, Machine learning, deep learning.

Contact: Christos Strydis